# CM108B/ CM119B/ HS-100B USB Audio Single Chip

## Application Notes

Ver. 1.5

Feb. 20th, 2023

### NOTICES

THIS DOCUMENT IS PROVIDED “AS IS” WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, DOCUMENT OR SAMPLE.

ALL RIGHTS RESERVED. NO PART OF THIS DOCUMENT MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS, ELECTRONIC OR MECHANICAL, INCLUDING INFORMATION STORAGE AND RETRIEVAL SYSTEMS, WITHOUT PERMISSION IN WRITING FROM THE C-MEDIA ELECTRONICS, INC.

---

### COPYRIGHT

Copyright © 2010-2014 C-Media Electronics Inc.

All rights reserved. All content included on this document, such as text, graphics, logos, button icons, images, audio clips, digital downloads, data compilations, and software, is either the exclusive property of C-Media Electronics Inc., its affiliates (collectively, “C-Media”), its content suppliers, or its licensors and protected by Republic of China and international copyright laws.

### TRADEMARKS

C-Media, the C-Media Logo, Xear 3D, Xear 3D Logo, Speaker Shifter, Smart Jack, and Smart Audio Jack, Middleware are trademarks of C-Media Electronics Inc. in Republic of China and/or other countries. All other brand and product names listed are trademarks or registered trademarks of their respective holders and are hereby recognized as such.

## TABLE OF CONTENTS

|                                                            |    |

|------------------------------------------------------------|----|

| Release Note .....                                         | 4  |

| 1 About this document.....                                 | 5  |

| 2 Typical System Block Diagram .....                       | 5  |

| 3 Schematics Design Notes.....                             | 6  |

| 3.1 EEPROM .....                                           | 6  |

| 3.2 Headphone Out for Cap-less Design .....                | 7  |

| 3.3 Power Control Design.....                              | 8  |

| 3.4 Crystal-less Design .....                              | 8  |

| 3.5 USB Interface Design .....                             | 9  |

| 4 Layout Guide.....                                        | 9  |

| 4.1 General Rules.....                                     | 10 |

| 4.2 Differential Signal Pair Impedance Matching .....      | 14 |

| 4.3 Layout design of Ground and Supply Plane geometry..... | 14 |

| 4.4 Decoupling and bypassing capacitors .....              | 15 |

| 4.5 The USB connector .....                                | 16 |

| 4.6 Guard ring on PCB-edges.....                           | 16 |

| 4.7 Crosstalk.....                                         | 18 |

| 4.8 Return Current and Loop Areas .....                    | 18 |

| 4.9 ESD Protection System Design Consideration .....       | 20 |

| 4.10 EMI Solutions Summery .....                           | 20 |

| 5 CM108AH/ CM119A/ HS-100 Transfer Guide .....             | 21 |

| 5.1 Crystal/ No Crystal .....                              | 21 |

| 5.2 REGV/ AREG36 .....                                     | 21 |

| 5.3 USB D+ Pull-up Resistor .....                          | 22 |

| 5.4 Microphone Input Design.....                           | 22 |

| 5.5 Recording mute LED flashing when IC power on .....     | 24 |

| 5.6 CM108B with CM Driver.....                             | 25 |

| Summary.....                                               | 25 |

## Release Note

| Revision | Date       | Description                                            |

|----------|------------|--------------------------------------------------------|

| 0.9      | 2013/10/04 | Preliminary release                                    |

| 1.2      | 2019/10/05 | Add ground planes recommendations                      |

| 1.3      | 2020/08/12 | Add mute LED flash on plug in                          |

| 1.4      | 2022/05/03 | Add<br>4.2 Differential Signal Pair Impedance Matching |

| 1.5      | 2023/02/20 | Add<br>5.6 CM108B with CM Driver                       |

## 1 About this document

This document summarizes the common application notes for customers who are designing their products with Cmedia CM108B/ CM119B/ HS-100B USB audio single chip solutions. It contains the system block diagram, schematics design notes, layout guide, and some other design notes. It's recommended to read this document before starting to plan and design products with CM108B/ CM119B/ HS-100B USB audio solution.

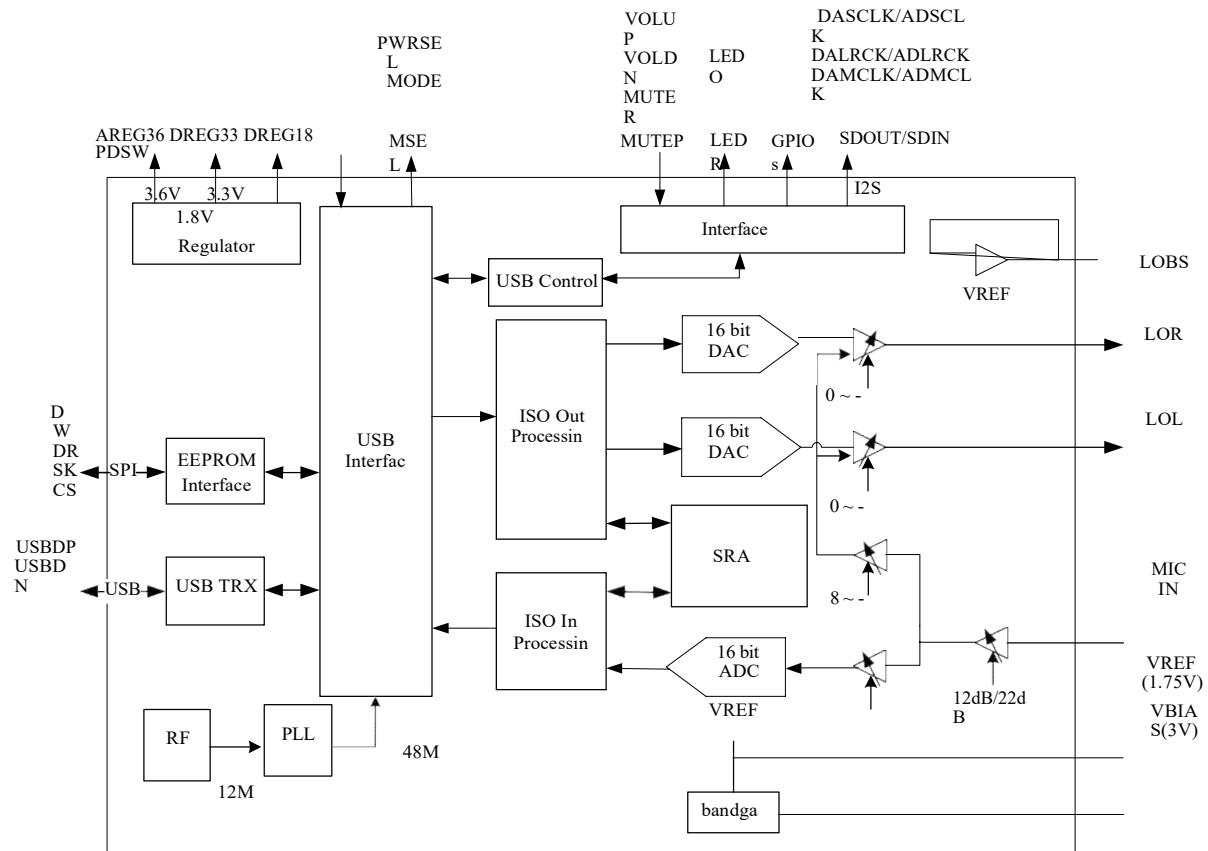

## 2 Typical IC Block Diagram

The typical IC block diagram is as following:

### 3 Schematics Design Notes

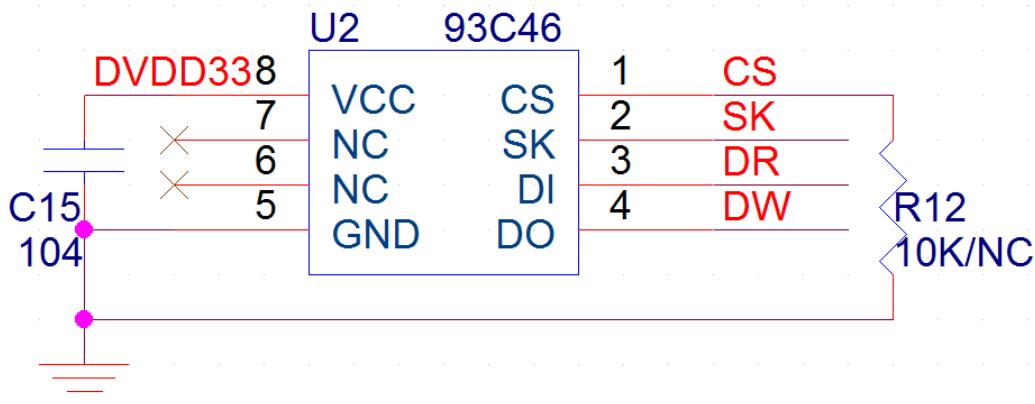

#### 3.1 EEPROM

CM108B/ CM119B/ HS-100B support EEPROM 93C46.

Multiple settings are available by changing the parameters of the EEPROM.

For more information, please refer to the EEPROM configuration tool and its user manual.

The 10K ohm resistor shown in the figure might need to be placed. It depends on the reference circuit in the datasheets of different EEPROM manufacturers.

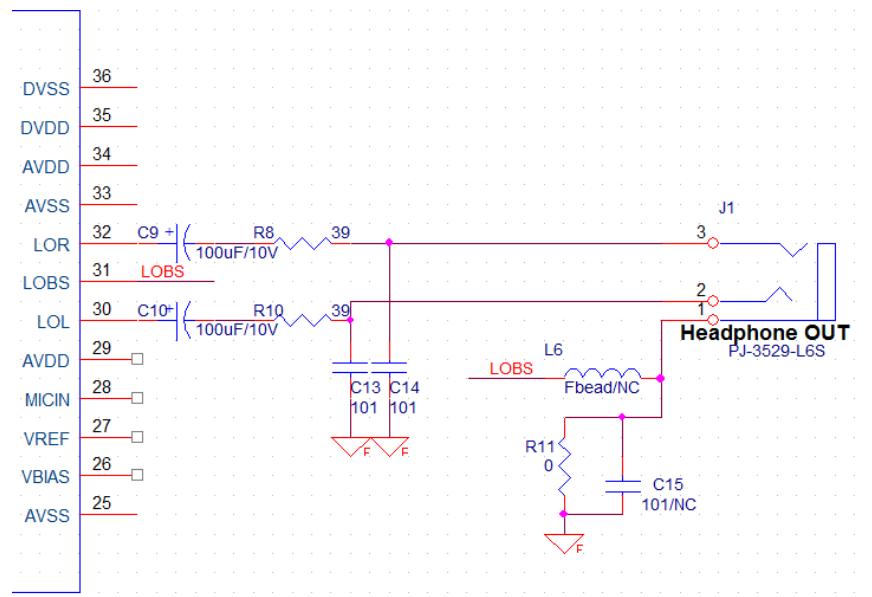

### 3.2 Headphone Out for Cap-less Design

CM108B/ CM119B/ HS-100B support Cap-less Outputs.

For lower capacitor component cost, C9 and C10 can be removed (short-circuited), and use cap-less line out as the schematics above. However, when using cap-less mode, the inter-channel crosstalk may be slightly higher (worse).

| Output Type | R11   | C15  | C9    | C10   | L6    |

|-------------|-------|------|-------|-------|-------|

| Normal      | Short | Open | 100uF | 100uF | Open  |

| Cap-less    | Open  | 101  | Short | Short | FBead |

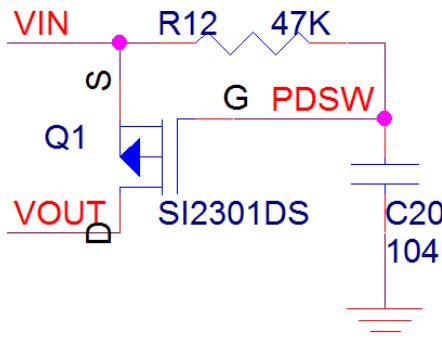

### 3.3 Power Control Design

PDSW power control supports DC 1.8V ~ 5V

| OS Mode   | PDSW state |

|-----------|------------|

| Operation | Drive Low  |

| Suspend   | Open       |

Please place a capacitor as C<sub>20</sub> for a more steady system if the external circuit requires a current more than 100 mA.

### 3.4 Crystal-less Design

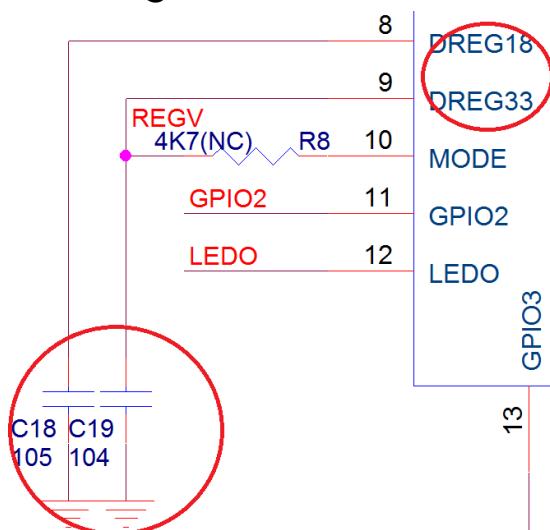

CM108B/ CM119B/ HS-100B embedded an internal cost effective oscillator. Therefore, no other external crystal or oscillator is needed. For better performance and steady system, please place a 1uF (105) capacitor for DREG18 and 0.1uF (104) for DREG33 regulator pins.

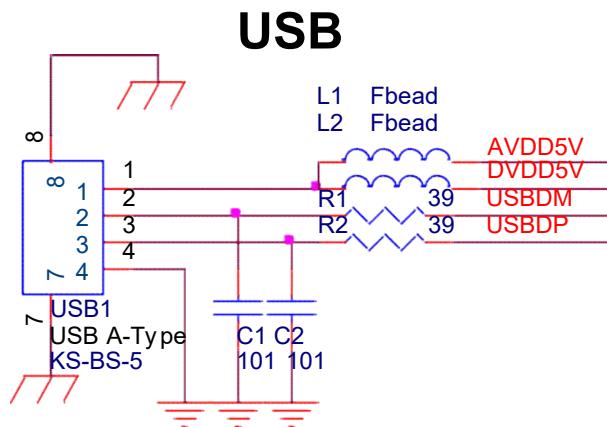

### 3.5 USB Interface Design

R1 & R2 are for USB PHY impedance matching.

C1 & C2, L1 & L2 are for EMI solution.

No pull up resistor is needed for USBDP since it's embedded in the internal PHY circuit

## 4 Layout Guide

This section provides guideline for the design of high integrated USB audio PCB. It's important to ensure maximum performance proper component placement and routing. This document includes properly isolated digital circuit and analog circuit. The effects of ground loop and supply plane geometry, decoupling/ bypassing/ filtering capacitors placement priorities, USB D+ and D- signals, analog power supplies, and analog ground planes.

## 4.1 General Rules

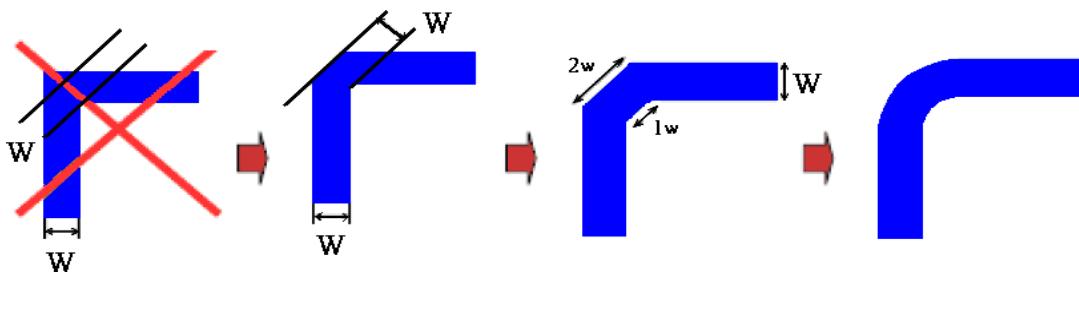

1. If a path has to turn  $90^\circ$ , it's better to separate the  $90^\circ$  into 2 turns by using two  $135^\circ$  turn (keep angles  $\geq 135^\circ$ ) or an arc instead of making a single  $90^\circ$  turn. It can reduce reflection on the signal by minimizing impedance discontinuities.

Turn Angle

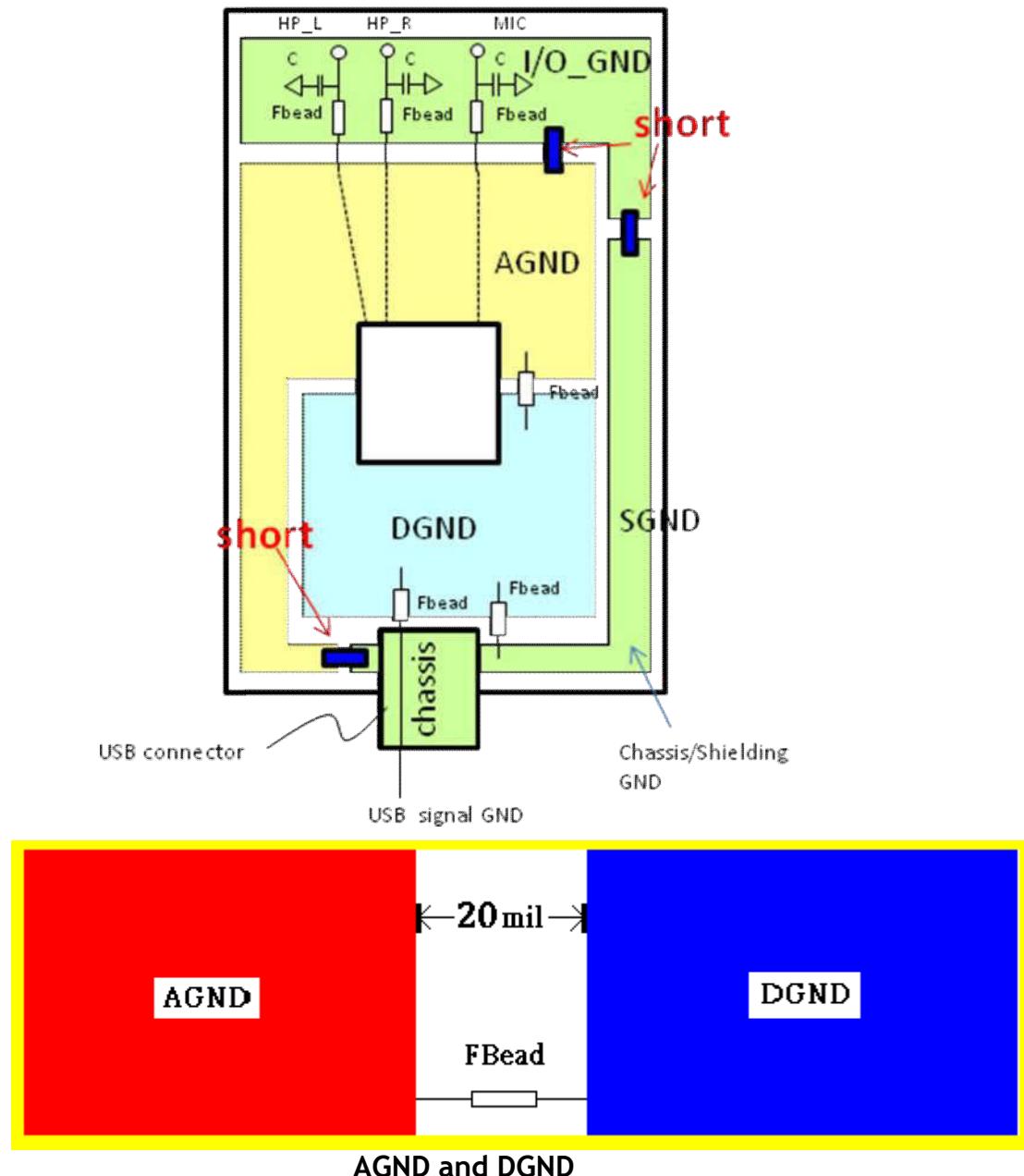

2. The old rules of splitting power and ground into “digital” and “analog” sections is necessary when doing an audio PCB layout. If possible, analog circuit and analog power should be put on Analog ground area, and digital ones are separate from the analog area.

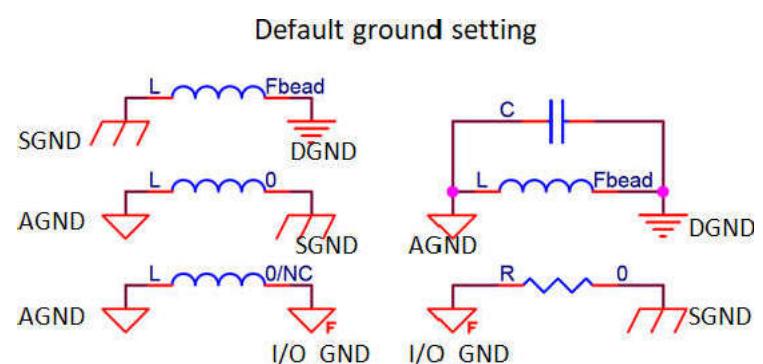

3. It is recommended to use 4 grounds when building a grounding system: AGND / DGND / USB Shielding ground (SGND) / IO ground (I/O\_GND). Use different ferrite beads or resistors to connect different ground planes when debugging EMI issues.

AGND: Analog GND

DGND:

Digital GND

SGND: System/Shielding GND

I/O\_GND: Phone Jack GND.

- A. Short between AGND and I/O\_GND, EMI could degrade, but crosstalk (between headphone out to microphone in) could improve

Adding a bead between AGND and IO\_GND, EMI could improve, but crosstalk (between headphone out to microphone in) could degrade

- B. Short between SGND and I/O\_GND, could improve ESD, but ground noise could induce from USB shielding

Adding a bead between SGND and I/O\_GND, could degrade ESD, but become less susceptible to USB shielding noise

- C. In some case, AGND and IO\_GND could be merged as AGND\*. Short between AGND\* and SGND could improve ESD, but could induce USB shielding noise, if shielding is not properly implemented

Adding a bead between AGND\* and SGND could degrade ESD, but become less susceptible to USB shielding noise

- D. By default DGND and AGND is connected by a bead, and provides better audio quality. However if the PCB size is small, or ground area is already small, DGND and AGND could be short together to increase ground plane and improve ESD. The side effect is reduced in audio quality.

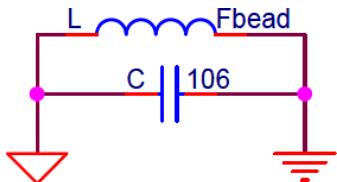

- E. As shown in the diagram below, the capacitor (e.g. 10uF) connected between DGND and AGND is to reduce EMI

In general if PCB size is very small (for example, implemented to fit into USB type-C connector), it is recommended to connect all the grounds together to be effective. If the PCB size is large enough, it is recommended to separate different ground planes and short only the necessary parts according to issues to overcome (e.g. ESD, EMI and crosstalk)

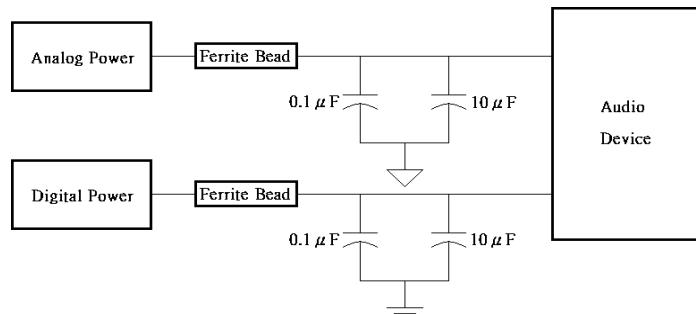

4. Connect analog and digital power planes at one point through a low impedance bridge or preferably through a ferrite bead.

5. To achieve proper ESD/EMI performance; it's suggested to use a 0.1uF capacitor on each cable PWR bus line to chassis GND close to the connector pin. If voltage regulators are used, place a 0.1μF capacitor on both input and output. This is to increase the immunity to ESD and reduce EMI.

**Figure6. Capacitors Array**

6. Do not route traces cross from one power/ ground plane to another. This can cause a broke n RF return path resulting in an EMI radiating loop. This is important for higher frequency or repetitive signals. Therefore, on a multi-layer board, it is best to run all clock signals on the signal plane above a solid ground plane.

## 4.2 Differential Signal Pair Impedance Matching

The USB D+ D- differential pairs, which can operate at a rate of 12Mbit/s, are some of the most critical signals on a PCB. Its implementation on the PCB requires special considerations. The inductive and capacitive reactance, resistance, and conductance of a PCB differential pair will determine the impedance of the trace pair at any point along the PCB track. The value of differential impedance will be a function of the physical dimensions of the trace, as detail below.

**Differential: Impedance of  $90\Omega$ , is optimal**

**Single-end: Impedance of  $45\Omega$ , is optimal**

## 4.3 Layout design of Ground and Supply Plane geometry

The layout separates the analog and digital ground planes with a 20 to 30 mils gap. The moat helps to isolate noisy digital circuit from clean analog audio circuit. The digital and analog ground planes are tied together by a wide link(about 30mils) at a point close to the USB connector. This will be the "drawbridge" that goes across the moat. Do not allow any digital or analog signal traces pass through the drawbridge. Otherwise, the digital noise may get into the analog signals and make audio performance worse.

In order to achieve the best audio performance and prevent crosstalk issue, C-Media recommend that the width of each I/O signal trace be at least 10 mils and the space be at least one time the size of the width of signal trace.

For a layout that helps to reduce noise, separating analog and digital ground planes is

needed. The digital components should be placed over the digital ground plane, and the analog components (including the analog power regulators) should be placed over the analog ground plane. In addition to ground planes scheme, digital and analog power supply planes should be partitioned directly over their ground planes. Place analog power coincident with analog ground and digital power coincident with digital ground. If any portion of analog and digital plane overlaps, the distributed capacitance between the overlapping portions will couple digital noise into the analog circuit. This defeats the purpose of isolating the power planes. The power and ground planes should be separated by approximately 40mils for the four layer PCB design. Using power and ground planes forming a natural, high capacitive, bypass capacitor to reduce overall PCB noise.

#### 4.4 Decoupling and bypassing capacitors

Bypass capacitors on the PCB are used to short digital noise to ground. Commonly, USB audio controller may generate noise when its internal digital circuit is operating. The current changes arise in the power and ground pins for the related section of the USB audio controller. The goal is to force AC current to flow in the shortest loop from the supply pin through the bypass cap and back into the USB audio controller through the nearby ground pin. A bypassing circuit is supposed to be a low lead inductance between the USB audio controller and the bypass capacitors when in the operating frequency of the USB audio controller. The long-trace will greater the inductance. To avoid long-trace inductance effects, use the shortest traces for bypass capacitors, with wide traces to reduce impedance. For the best performance, use supply bypass leads of less than one-half inch.

The USB audio controller power supply pins are need the bypass caps, which are located as close as possible to the supply pins. The capacitors must have low inductance and low equivalent series resistance (ESR). Tantalum 10 $\mu$ F surface mount devices are good if they are used in conjunction with 0.1 $\mu$ F ceramics. The filter capacitors with "B" priority, the reference filter to stabilize the reference voltage for internal Ops and reference output filters should be placed close to USB audio controller. A good reference voltage is relative to good analog performance. These decoupling capacitors should be close to the USB audio controller pins (Audio input pin), or positioned for the shortest connections to pins, with wide traces to reduce impedance.

#### 4.5 The USB connector

Place the USB device and connector on the un-routed board first. With minimum trace lengths, as equal as possible (D+, D-), route high-speed clock and USB differential signal pair first. Keep the distance between high-speed signals to USB differential signal pair far. Route the USB differential signal pair using a minimum of vias and corners. It can reduce signal reflection and impedance change. If it's necessary to turn 90°, it's better to use two 45° turn or an arc instead of making a single 90° turn. It can reduce reflection on the signal by minimizing impedance discontinuities.

Please don't route USB differential signal pair trace under crystal, oscillator, clock synthesizers, magnetic devices or ICs. It will cause interference. Stubs on USB differential signal pair should be avoided. While stubs exist, it will cause signal reflection and lower the quality. If a stub is unavoidable in the design, no stub should be bigger than 200mils.

#### 4.6 Guard ring on PCB-edges

The major advantage of a multilayer PCB with ground-plane is the ground return path below each and every signal or power trace. As shown in Figure 10 the field lines of the signal return to PCB ground as long as an "infinite" ground is available. Traces near the PCB-edges do not have this "infinite" ground and therefore may radiate more than others. Thus signals (e. g. clocks) or power traces (e.g. core power) identified to be critical should not be routed in the vicinity of PCB-edges, or - if not avoidable - should be accompanied by a guard ring on the PCB edge.

Figure12. The field lines of the signal return to PCB ground

The intention of the guard ring is that HF-energy, that otherwise would have been emitted from the PCB-edge, is reflected back into the board where it partially will be absorbed. For this purpose ground traces on the borders of all layers (including power layer) should be applied as shown in Figure 10. As these traces should have the same (HF) potential as the ground plane they must be connected to the ground plane at least every 10 mm.

#### Advantages of power planes

1. Easy and fast to implement

2. Low inductive power supply

3. Creates a capacity together with ground plane

#### Advantages of routed power supplies

1. Allows the usage of one layer for more than one supply system, thereby reducing the crosstalk between these supplies

2. May reduce cross-talk within each supply system

3. Requires more careful power routing

4. Higher supply impedance may require extra capacity for supply stabilization.

## 4.7 Crosstalk

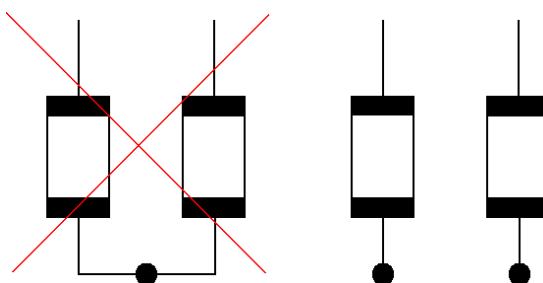

A VIA has a considerable impedance

As any trace also a VIA has a considerable impedance. Therefore, VIAs of critical circuits such as decoupling circuits must be exclusive for this circuit. The 2 parts of next Figure indicate how a shared VIA causes cross-talk between the involved circuits. The right most part shows the correct wiring.

**Figure13.** Bad Screw hole to Cross Talk

## 4.8 Return Current and Loop Areas

Return path or image planes provide low impedance, shortest possible path for return signal currents. The best image plane is the ground plane for the C-Media PCI Express board.

Do not route traces so they cross from one plane to the other. This can cause a broken RF return path resulting in an EMI radiating loop. This is important for higher frequency or repetitive signals. Therefore, on a multi-layer board, it is best to run all

clock signals on the signal plane above a solid ground plane.

Avoid crossing the image power or ground plane boundaries with high-speed clock signal traces immediately above or below the separated planes. This also holds true for the twisted pair signals. Any unused area of the top and bottom signal layers of the PCB can be filled with copper that is connected to the ground plane.

An electrical circuit must always be a closed loop. Up to now, only the signal path was discussed but not the path back to the source - the return current. With DC, the return current takes the way back with the lowest resistance. With a higher frequency, the return current flows along the lowest impedance. This is directly beside the signal.

If this return path, mostly the ground plane, has a slot, the return current has to take another way and the results in a loop area. The larger the area, the more radiation and EMI problems occur. The designer has to make sure that the return current can flow directly underneath the signal trace. Another is to route the signal the same way as the return current flows. The best solution is to avoid any slots in the d reference plane.

## 4.9 ESD Protection System Design Consideration

ESD protection system design consideration is covered CM108B/ CM119B/ HS-100B itself.

The following are additional considerations for ESD protection in a system.

- Metallic shielding for both ESD and EMI

- Chassis GND isolation from the board GND

- Air gap designed on board to absorb ESD energy

- Clamping diodes to absorb ESD energy

- Capacitors to divert ESD energy

## 4.10 EMI Solutions Summery

EMI issues can be very knotty and not easy to solve. However, with some tips and experience, it would be relatively easy when the debugger has some clues. Some tips are listed below for those who are dealing with EMI issues when making a USB audio device PCB layout.

- Build a 4-grounds ground system: AGND/DGND/IO\_GND/USB Shielding GND and reserve a pad for resistor or fbead.

- Place at least a resistor/fbead pad for each analog output, since the EMI noise may be easily delivered through DAC paths.

- If the frequency of measured over-limit-EMI-signal is 12MHz or its multiple (e.g. 36MHz/108MHz/132 MHz), it's more likely caused by the USB signal. Therefore, instead of modifying audio output/input paths, USB PHY related circuit needs to be considered.

## 5 CM108AH/ CM119A/ HS-100 Transfer Guide

For those who are currently manufacturing products with CM108AH/ CM119A/ HS-100, this section highlights the parts that need to be noticed of the schematics.

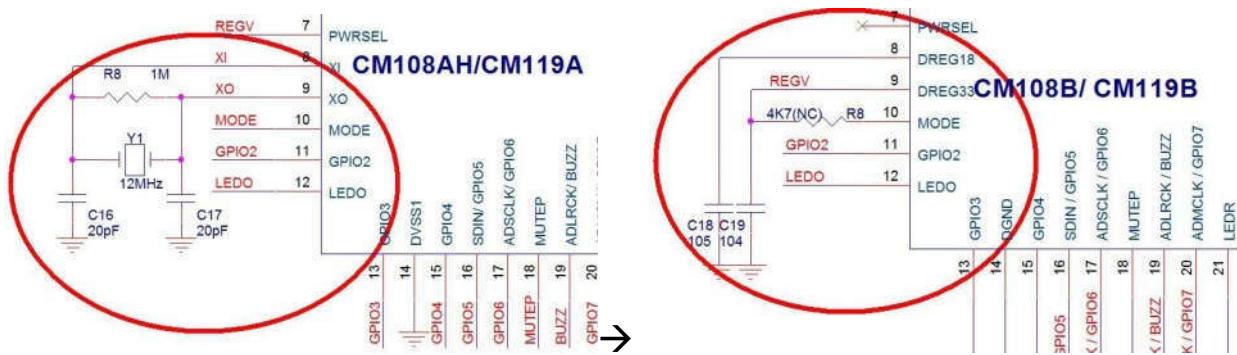

### 5.1 Crystal/ No Crystal

CM108B/ CM119B/ HS-100B uses internal cost effective oscillator, so PCBs designed for CM108AH/ CM119A/ HS-100 transferring to new CM108B/ CM119B/ HS-100B doesn't need an external 12MHz crystal oscillator. The original pins are replaced by digital regulator pins (3.3V & 1.8V) for external capacitors for steadier system. The differences and schematic modification of this part is shown in the following figures below.

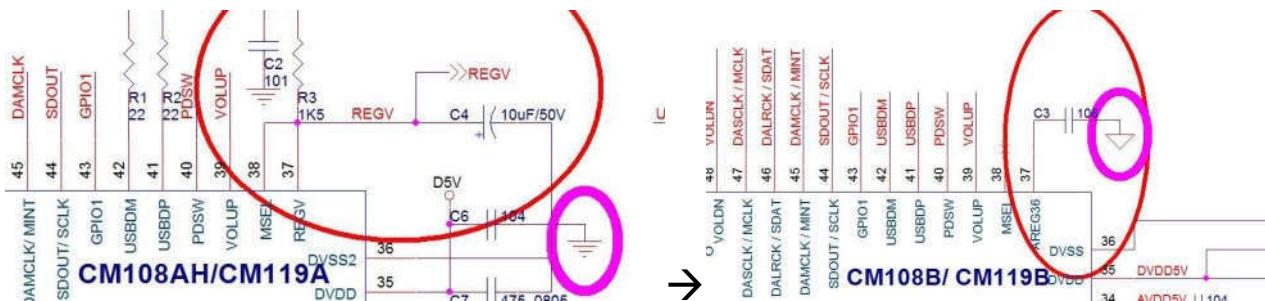

### 5.2 REGV/ AREG36

CM108AH/ CM119A/ HS-100 has an external regulator 3.3V output pin, while CM108B/ CM119B/ HS-100B replaced it with analog 3.6V regulator for better audio quality and performance.

Device still work properly if CM108B/ CM119B/ HS-100B replaces the CM108AH/ CM119A/ HS-100 without any modifications, but it is highly recommended that new projects or new PCBs uses new layout for better audio quality performance. The difference of this part is shown in the figures below.

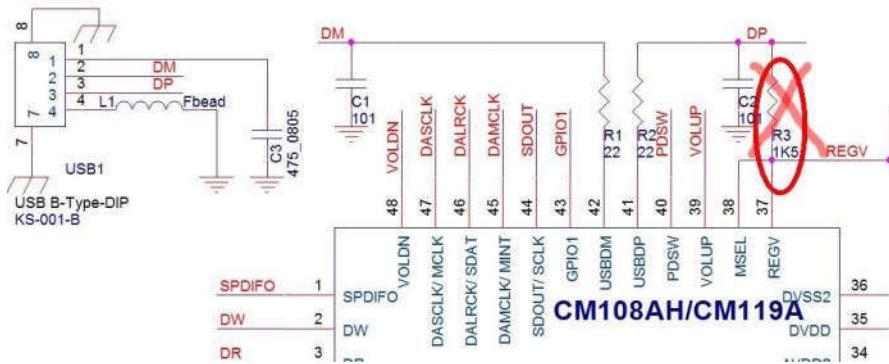

### 5.3 USB D+ Pull-up Resistor

When using CM108B/ CM119B/ HS-100B, the pull up resistor for USB D+ is not needed. The pull-up circuit is embedded in the USB PHY already.

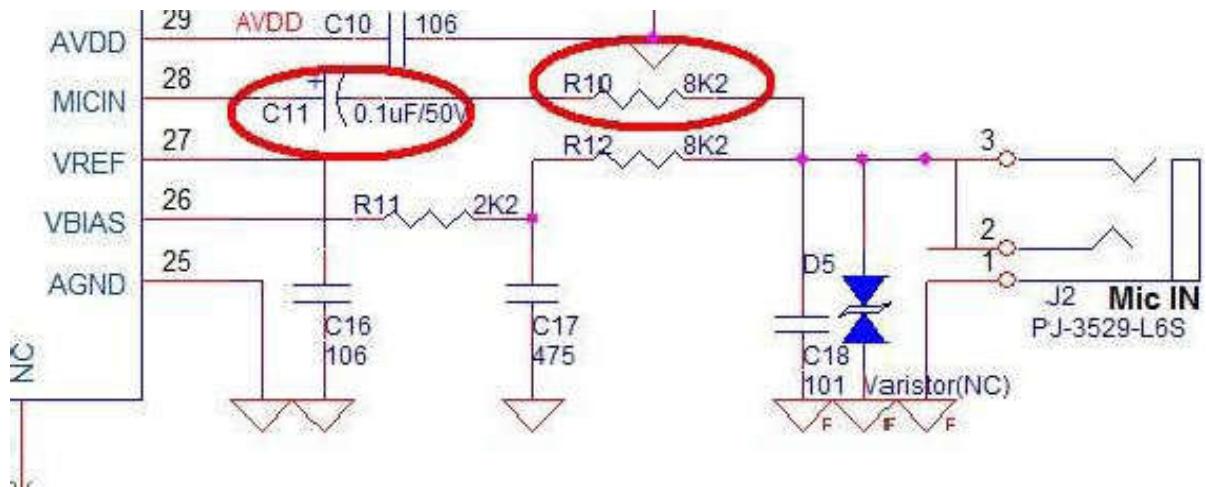

### 5.4 Microphone Input Design

CM108B/ CM119B/ HS-100B improved its ADC (MIC) performance, and it also has better sensitivity for microphones. For better voice recording quality, an 8.2K ohm resistor and a 0.1uF capacitor are placed (series connection) in the MIC path. The value of the resistor and capacitor may be slightly different for different PCB layout and microphones. Please follow the reference schematic for microphone section design.

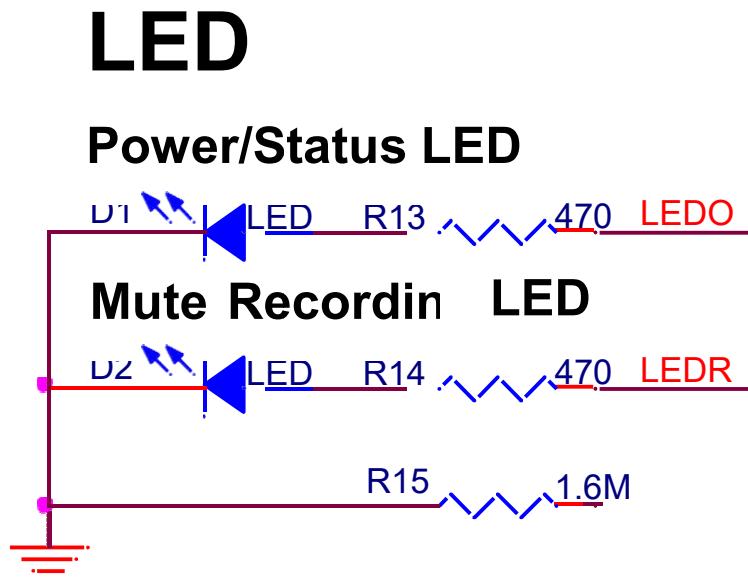

## 5.5

Add R15 for recording mute LED flashing when IC power on.

## 5.6 CM108B with CM Driver

When CM108B needs to use the CM driver,

Pin13(GPIO3)/Pin15(GPIO4)/Pin43(GPIO1) must be pulled high

## Summary

The differences of CM108AH/ CM119A/ HS-100 and CM108B/ CM119B/ HS-100B are summarized in the table below. Please check this table when designing products with CM108B/ CM119B/ HS-100B.

|         | PIN 7  | Parts                    | PIN 8  | Parts          | PIN 9  | Parts                    |

|---------|--------|--------------------------|--------|----------------|--------|--------------------------|

| HS-100B | DREG18 | 105                      | DREG33 | 104            |        |                          |

| HS-100  | XI     | 20p/1M to XTAL           | XO     | 20p/1M to XTAL |        |                          |

| CM108B  |        |                          | DREG18 | 105            | DREG33 | 104                      |

| CM108AH |        |                          | XI     | 20p/1M to XTAL | XO     | 20p/1M to XTAL           |

| CM119B  |        |                          | DREG18 | 105            | DREG33 | 104                      |

| CM119A  |        |                          | XI     | 20p/1M to XTAL | XO     | 20p/1M to XTAL           |

|         | PIN 37 | Parts                    | PIN 39 | Parts          | PIN 40 | Parts                    |

| HS-100B |        |                          | AVDD36 | 106 to AGND    |        |                          |

| HS-100  |        |                          | REGV   | 106 to DGND    |        |                          |

| CM108B  | AVDD36 | 106 to AGND              |        |                | PDSW   | 104                      |

| CM108AH | REGV   | 106 to DGND              |        |                | PDSW   |                          |

| CM119B  | AVDD36 | 106 to AGND              |        |                | PDSW   | 104                      |

| CM119A  | REGV   | 106 to DGND              |        |                | PDSW   |                          |

|         | PIN 41 | Parts                    | PIN 42 | Parts          | PIN 43 | Parts                    |

| HS-100B |        |                          | PDSW   | 104            | USBDP  | no need pull up resistor |

| HS-100  |        |                          | PDSW   |                | USBDP  | 1.5K to REGV pull up     |

| CM108B  | USBDP  | no need pull up resistor |        |                |        |                          |

| CM108AH | USBDP  | 1.5K to REGV pull up     |        |                |        |                          |

| CM119B | USBDP | no need pull up resistor |  |  |  |  |

|--------|-------|--------------------------|--|--|--|--|

| CM119A | USBDP | 1.5K to REGV pull up     |  |  |  |  |

**C-MEDIA ELECTRONICS INC.**

6F., 100, Sec. 4, Civil Boulevard, Taipei, Taiwan 106 R.O.C.

TEL: 886-2-8773-1100

FAX: 886-2-8773-2211

E-MAIL: sales@cmedia.com.tw

**Disclaimer:**

Information furnished by C-Media Electronics Inc. is believed to be accurate and reliable. However, no responsibility is assumed by C-Media Electronics Inc. for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications are subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of C-Media. Trademark and registered trademark are the property of their respective owners.